# CAPÍTULO 7 CONTADORES

- Introdução

- Contadores Assíncronos (Ripple)

- MOD número

- Divisão de Frequência

- Atraso de propagação nos contadores assíncronos

- Contadores Síncronos

- Contadores com MODnumber < 2<sup>N</sup>

- Contadores Síncronos DOWN e UP/DOWN

- Contadores com PRESET

- Contadores UP/DOWN com PRESET

- Arranjos Multi-estágios

- Decodificando um Contador

- Análise de Contadores Síncronos com flip-flops JK e D

- Exercícios

# Introdução

- No Capítulo 5 nós vimos os contadores e registradores básicos usando apenas flip-flops

- Vamos ver neste capítulo como podemos combinar flipflops e portas lógicas e obter diferentes tipos de contadores e registradores

- Vamos revisitar os contadores assíncronos

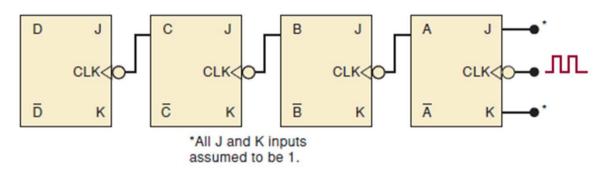

- Nos contadores assíncronos, o sinal de clock é aplicado apenas ao primeiro flip-flop

- A saída do primeiro flip-flop será o clock do segundo e assim por diante

# Contadores Assíncronos (Ripple)

# Contadores Assíncronos (Ripple)

#### **Exemplo:**

Um contador é necessário para contar o número de itens que passam por uma esteira em uma fábrica. Uma fotocélula e um feixe de luz são usados para gerar um pulso único cada vez que um item passa pelo local. O contador deve permitir a contagem de pelo menos 1000 objetos. Quantos flip-flops são necessários?

#### Resposta:

$2^{N} > 1000$

Como  $2^9 = 512$ , 9 flip-flops não são suficientes.

$2^{10} = 1024$

Portanto, são necessários 10 flip-flops

# Contadores Assíncronos (Ripple)

#### **Exemplo:**

Um contador assíncrono com 4 flip-flops começa no estado 0000 e em seguida um sinal de clock é aplicado. Algum tempo depois, o sinal de clock é removido e o contador mostra 0011. Quantos pulsos de clock ocorreram?

#### Resposta:

A resposta não é necessariamente 3.

O contador pode ter zerado 1, 2, 3, ... N vezes.

Portanto poderia ser 19, 35, 51, ou 19978403 pulsos

## MOD número

- O contador apresentado também é chamado de MOD número

- Neste caso, número = 2<sup>4</sup>

- É um contador assíncrono MOD-16

- Em geral um contador com N flip-flops é MOD 2<sup>N</sup>

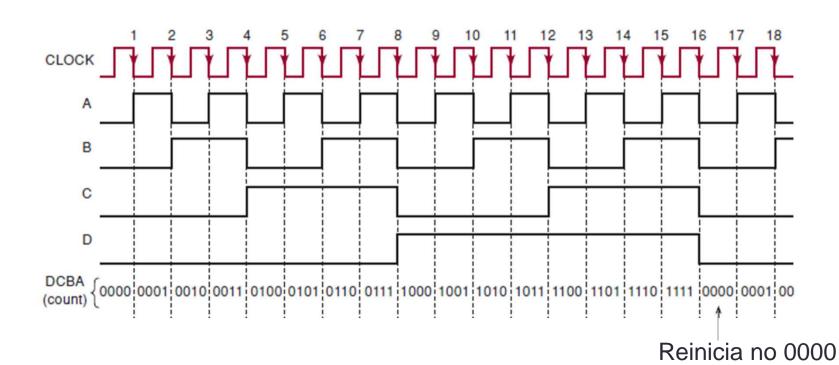

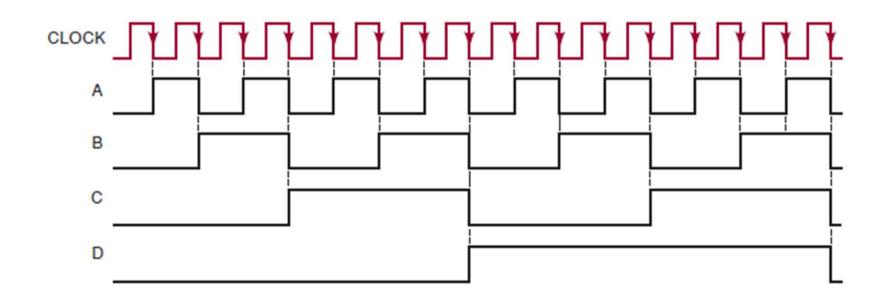

# Divisão de Frequência

- Como foi visto no Cap. 5, após cada FF em um contador, a freqência é a metade da frequência do seu clock

- No exemplo dado com 4 bits (MOD-16), se a frequência do clock de entrada for 16 KHz, na saída do último flipflop teremos 1 KHz.

- De modo geral:

- Em qualquer contador, o sinal da saída do último flip-flop (isto é, o MSB) terá frequência igual à frequência do clock de entrada dividido pelo número MOD do contador.

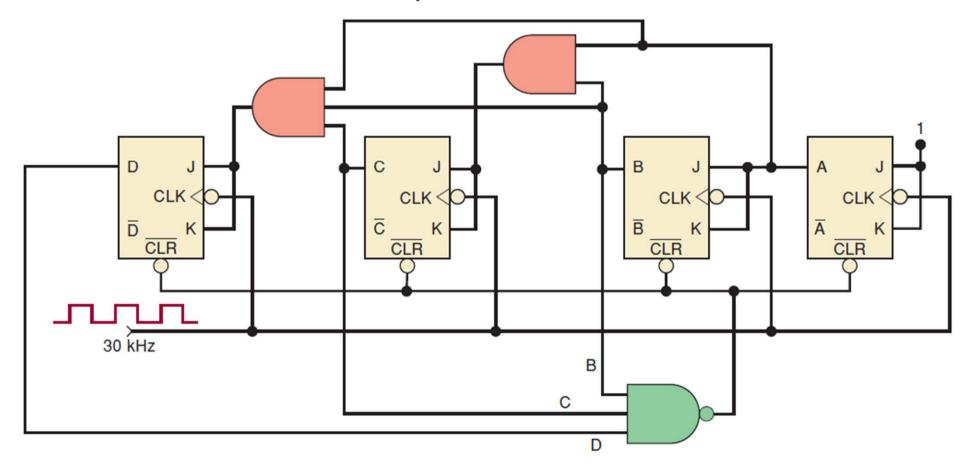

## Divisão de Frequência

- Por exemplo:

- No contador MOD 16, a frequência do último flip-flop do contador será 1/16 da frequência do clock.

## Divisão de Frequência

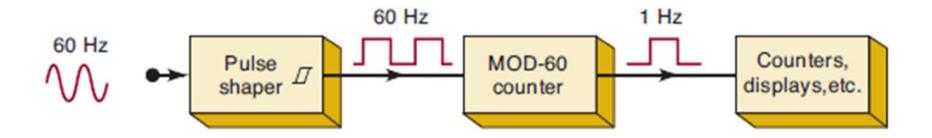

Exemplo:

Construção de um relógio digital

Precisamos de um método para obtermos um contador onde o MOD número seja menor que 2<sup>N</sup>

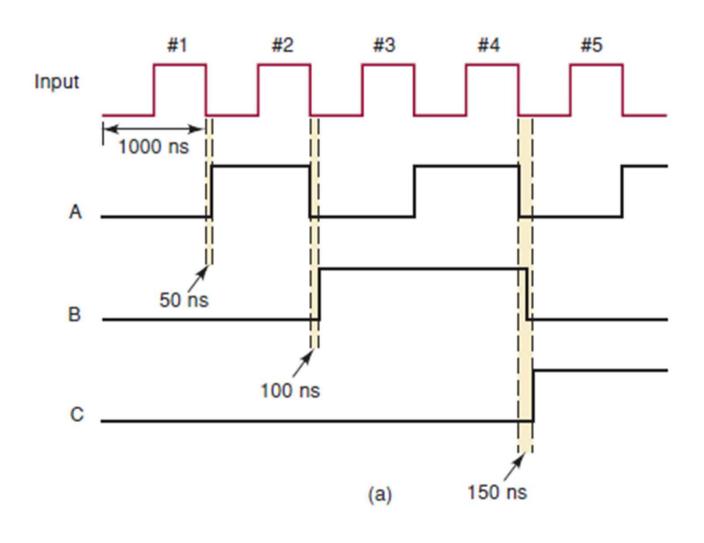

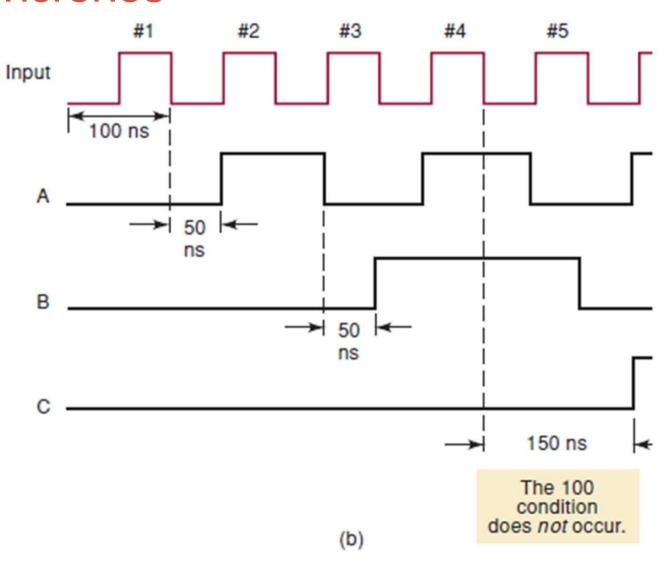

- Cada flip-flop tem um atraso de propagação (tpd) que é o tempo desde a ativação pelo clock (transição de subida ou de descida) até a mudança da saída Q.

- Como nos contadores assíncronos cada flip-flop ativa o flip-flop seguinte, o atraso total será Nxtpd.

- O tempo de propagação de flip-flops varia de 10 a 50 ns

- Surgem também os "glitches" que são estados fora da sequência predeterminada para o contador.

O problema do slide anterior pode ser evitado se o período do clock for grande o suficiente. A frequência máxima deve considerar o atraso dos N flip-flops

$$T_{

m clock} \ge N imes t_{

m pd}$$

$$f_{

m max} = \frac{1}{N imes t_{

m nd}}$$

$$f_{

m max} = \frac{1}{4 imes 24 \,

m ns} = 10.4 \,

m MHz$$

$$f_{

m max} = \frac{1}{6 imes 24 \,

m ns} = 6.9 \,

m MHz$$

#### Questões de Revisão

- Explique por que a limitação de frequência máxima diminui quanto mais flip-flops são adicionados

- Um certo flip-flop JK tem tpd = 12ns. Qual é o maior número MOD do contador que pode operar a 10 MHz?

- São contadores em que todos os flip-flops são disparados ao mesmo tempo, com o mesmo clock.

- O atraso não fica multiplicado por N

- Desvantagem: há necessidade de hardware extra: portas lógicas além dos flip-flops

- A regra básica de projeto de contadores síncronos é:

- Um contador síncrono deve ativar o modo "toggle" de um flip-flop somente quando todos os flip-flops de ordem menor estiverem em nível lógico alto.

- Atraso de propagação:

total delay = FF

$$t_{pd}$$

+ AND gate  $t_{pd}$

- Cis:

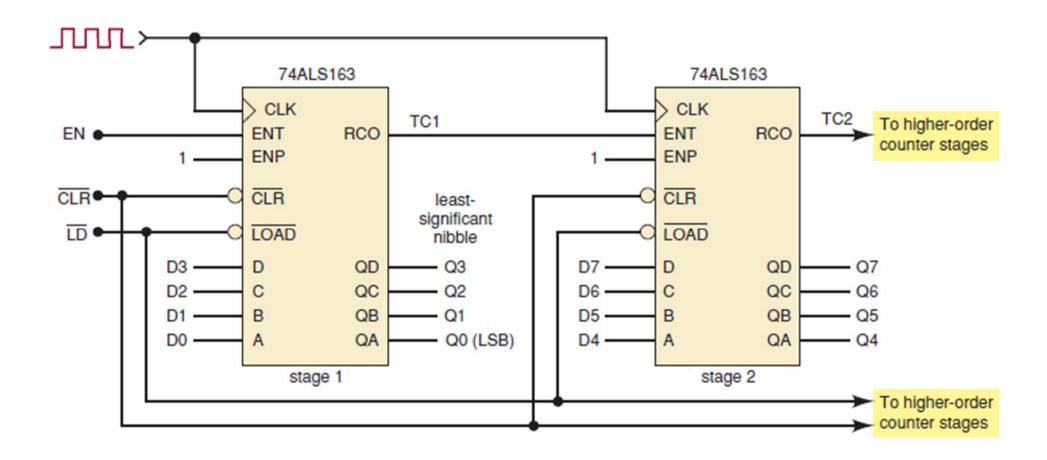

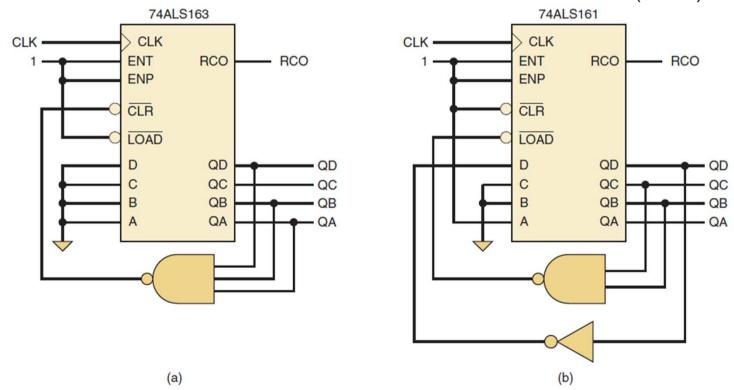

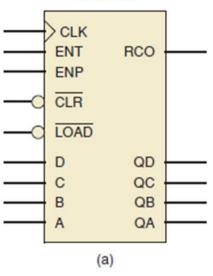

- 74LS160/74LS162: contador síncrono modulo 10

- 74LS161/74LS163: contador síncrono módulo 16

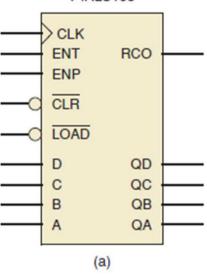

#### BCD DECADE COUNTERS/ 4-BIT BINARY COUNTERS

The LS160A/161A/162A/163A are high-speed 4-bit synchronous counters. They are edge-triggered, synchronously presettable, and cascadable MSI building blocks for counting, memory addressing, frequency division and other applications. The LS160A and LS162A count modulo 10 (BCD). The LS161A and LS163A count modulo 16 (binary.)

The LS160A and LS161A have an asynchronous Master Reset (Clear) input that overrides, and is independent of, the clock and all other control inputs. The LS162A and LS163A have a Synchronous Reset (Clear) input that overrides all other control inputs, but is active only during the rising clock edge.

|                    | BCD (Modulo 10) | Binary (Modulo 16) |

|--------------------|-----------------|--------------------|

| Asynchronous Reset | LS160A          | LS161A             |

| Synchronous Reset  | LS162A          | LS163A             |

- Synchronous Counting and Loading

- Two Count Enable Inputs for High Speed Synchronous Expansion

- · Terminal Count Fully Decoded

- Edge-Triggered Operation

- Typical Count Rate of 35 MHz

- ESD > 3500 Volts

SN54/74LS160A SN54/74LS161A SN54/74LS162A SN54/74LS163A

4-BIT BINARY COUNTERS

LOW POWER SCHOTTKY

J SUFFIX CERAMIC CASE 620-09

N SUFFIX PLASTIC CASE 648-08

#### **Exemplo:**

Determine  $f_{max}$  para o contador síncrono da figura anterior se o  $t_{pd}$  de cada FF é 50ns e o  $t_{pd}$  de cada porta AND é 20ns. Compare esse  $f_{max}$  com o  $f_{max}$  de um contador assíncrono.

#### Resposta:

Devemos considerar o  $t_{pd}$  do FF e da porta AND:

$$T_{\rm clock} \ge 50 + 20 = 70 \, \rm ns$$

Para o contador síncrono:

$$f_{\text{max}} = \frac{1}{70 \text{ ns}} = 14.3 \text{ MHz}$$

Para o contador assíncrono:

$$f_{\text{max}} = \frac{1}{4 \times 50 \,\text{ns}} = 5 \,\text{MHz}$$

- No exemplo anterior, o que precisa ser feito para transformá-lo em um contador MOD-32?

- Quais são as frequências máximas para os dois casos?

#### Resposta:

- Para transformar em MOD-32 basta que um quinto FF seja adicionado, com uma porta AND de 4 entradas ligadas nas saídas Qs dos FFs anteriores

- Para o contador síncrono, a frequência máxima será a mesma (14,3 MHz)

- Para o contador assíncrono, a frequência máxima será:

$$f_{max} = \frac{1}{5 \times 50ns} = 4MHz$$

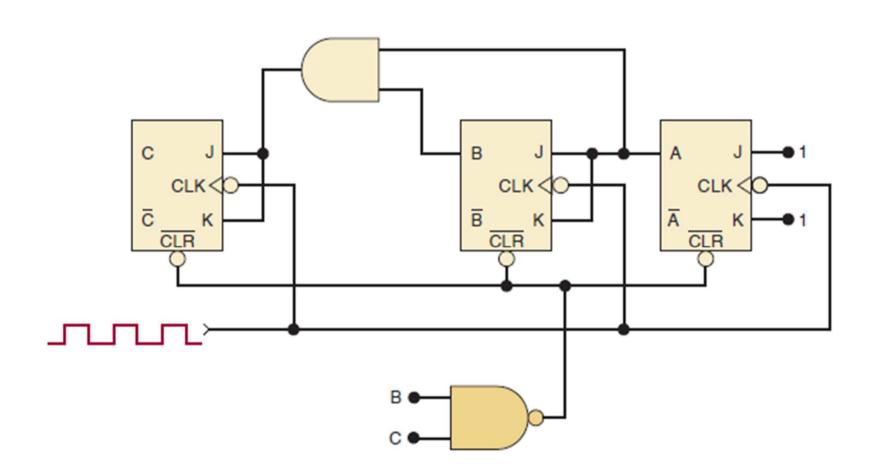

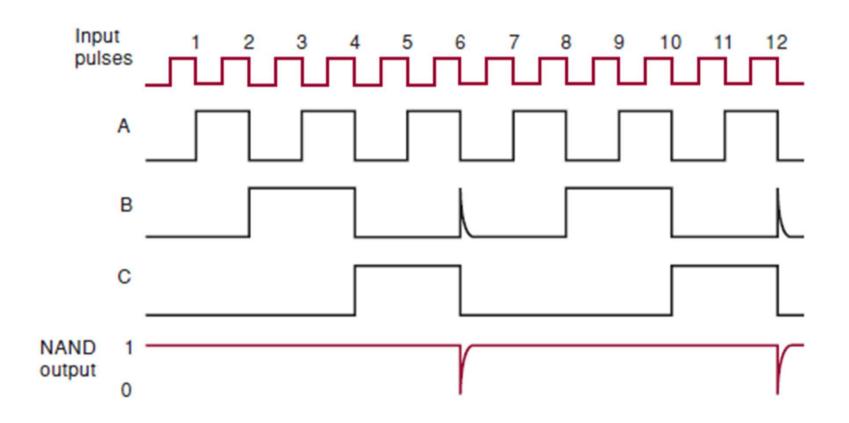

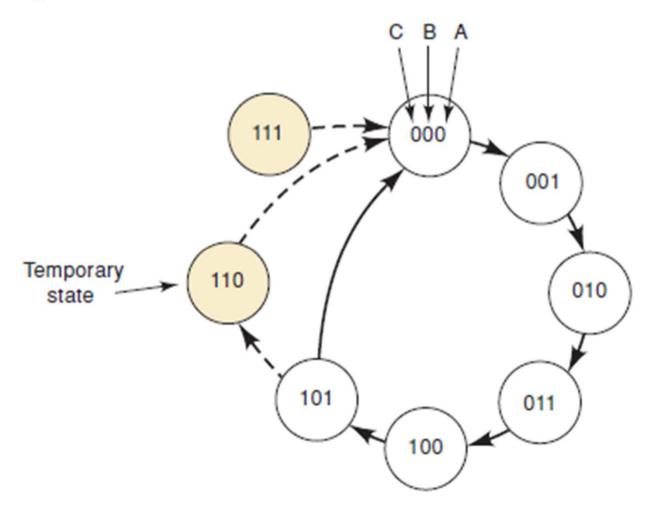

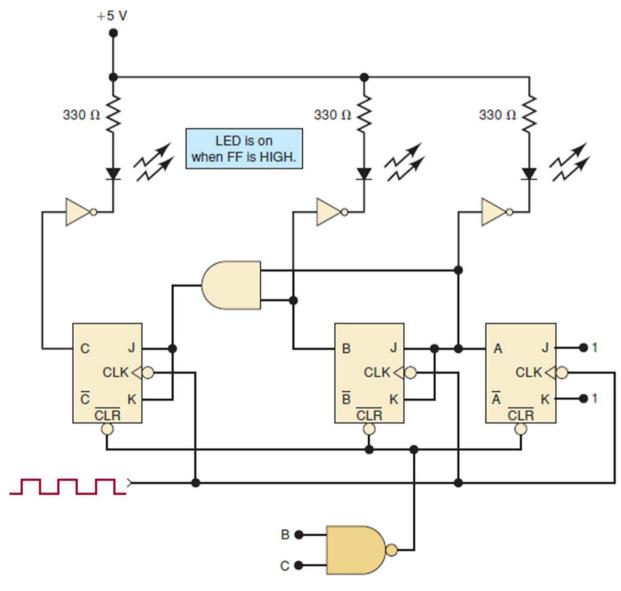

Diagrama de Estados

#### Exemplo:

#### Na figura anterior:

- (a) Qual será o estado dos LEDs quando o contador está armazenando a contagem de 5?

- (b) O que os LEDs vão mostrar quando o clock aplicado ao contador tiver a frequência de 1kHz?

- (c) O estado 110 será visível nos LEDs?

#### Resposta:

- (a) Como 5<sub>10</sub> = 101<sub>2</sub>, os LEDs estarão: LIGADO, DESLIGADO, LIGADO

- (b) Com a frequência de 1kHz, os LEDs estarão ligando e desligando tão rápido que para a vista humana vão parecer constantemente acesos, embora com uma intensidade reduzida

- (c) Não. O estado 110 persiste por apenas alguns nanosegundos ao retornar para o estado 000

Exemplo: Determine o MOD número para a figura abaixo.

Determine também a frequência na saída D.

Exemplo: Construa um contador MOD-10 (contador de década)

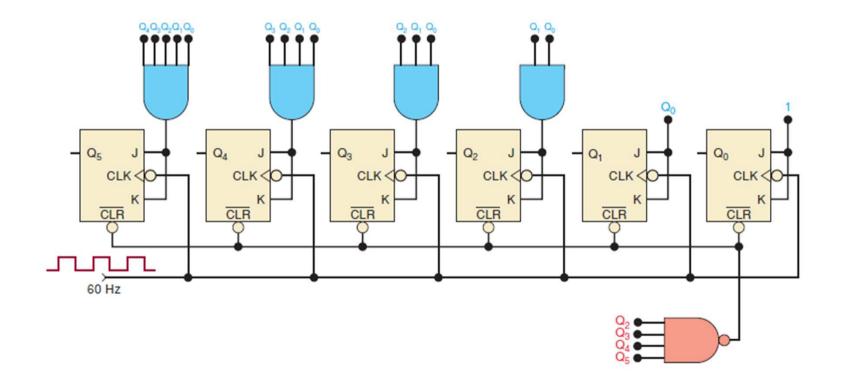

Exemplo: No exemplo do relógio digital, um contador MOD-60 era necessário para dividir a frequência de 60 Hz até 1Hz. Construa esse contador.

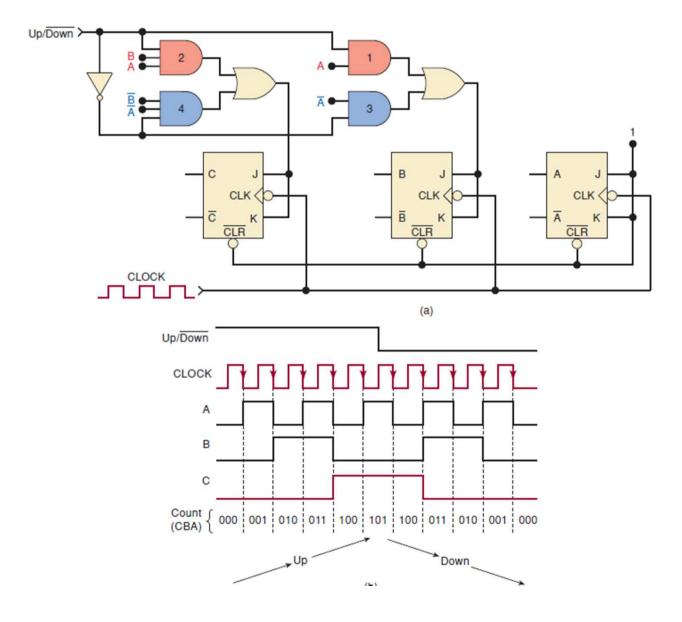

# Contadores Síncronos DOWN e UP/DOWN

Um contador decrescente (DOWN) utiliza as saídas Q invertidas para controlar as entradas J K (toggle):

## Contador UP/DOWN

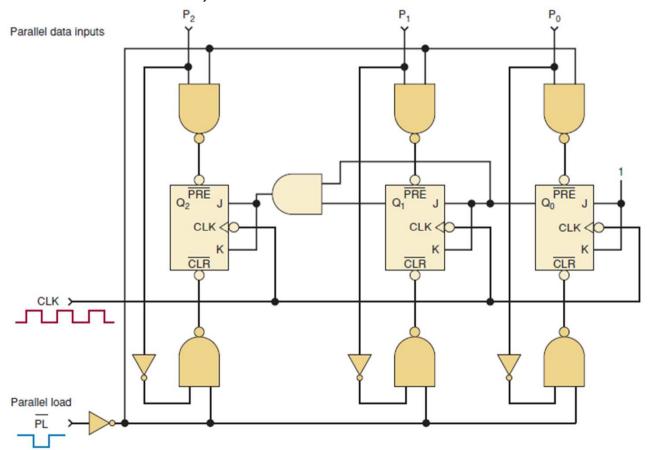

- O circuito abaixo é um contador com PRESET assíncrono

- Também existem os contadores com PRESET síncronos (ex.: 74LS160,161,162,163)

| Part<br>Number | Modulus |  |  |  |

|----------------|---------|--|--|--|

| 74ALS160       | 10      |  |  |  |

| 74ALS161       | 16      |  |  |  |

| 74ALS162       | 10      |  |  |  |

| 74ALS163       | 16      |  |  |  |

| (b)            |         |  |  |  |

#### 74ALS160-74ALS163 Function Table

| CLR | LOAD | ENP | ENT | CLK | Function      | Part Numbers        |

|-----|------|-----|-----|-----|---------------|---------------------|

| L   | X    | X   | X   | X   | Asynch. Clear | 74ALS160 & 74ALS161 |

| L   | X    | X   | X   | 1   | Synchr. Clear | 74ALS162 & 74ALS163 |

| Н   | L    | X   | X   | 1   | Synchr. Load  | All                 |

| Н   | Н    | Н   | Н   | 1   | Count up      | All                 |

| Н   | н    | L   | X   | X   | No change     | All                 |

| Н   | Н    | X   | L   | X   | No change     | All                 |

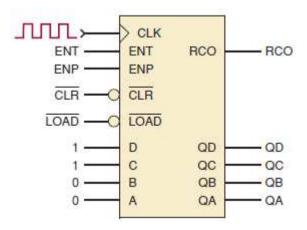

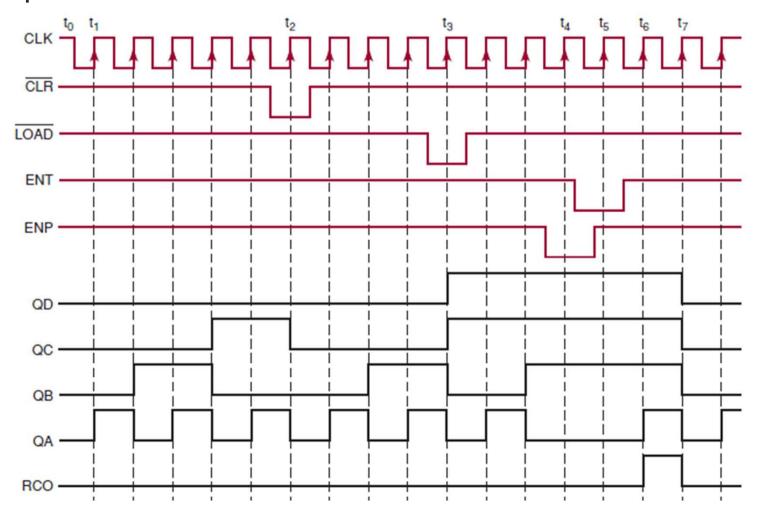

- Exemplo: Um contador 74LS163 tem as entradas dadas pelo diagrama de tempo dado. A entrada de dados paralela está permanentemente ligada a 1100. Assuma que o contador começa em 0000. Determine as formas de onda de saída do contador.

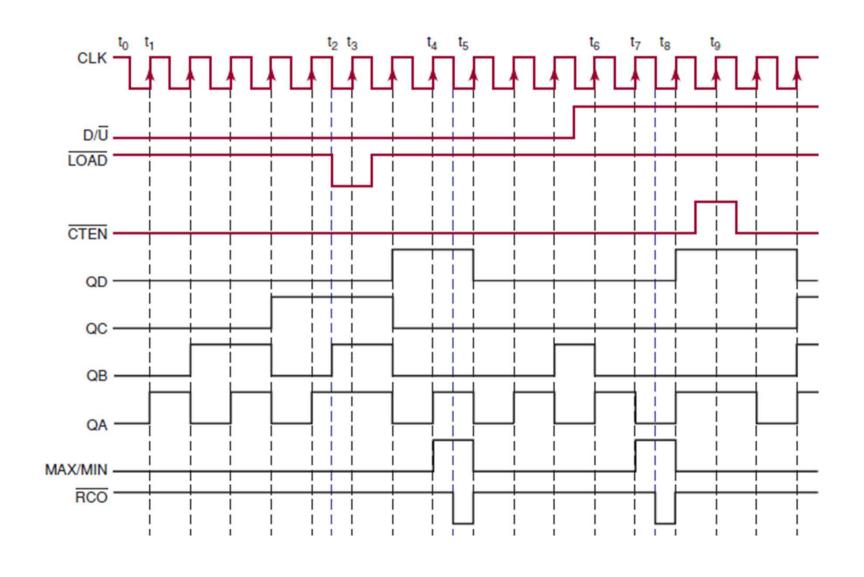

- A saída RCO fica ativa quando o contador chega no final da contagem

#### Resposta:

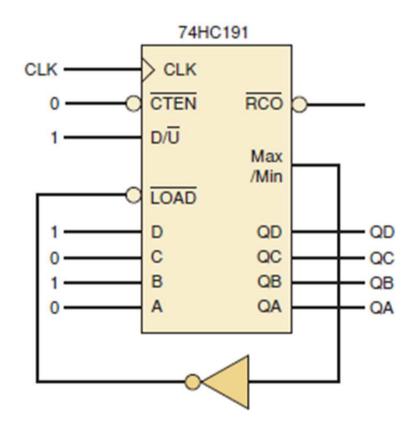

### Contadores UP/DOWN com PRESET

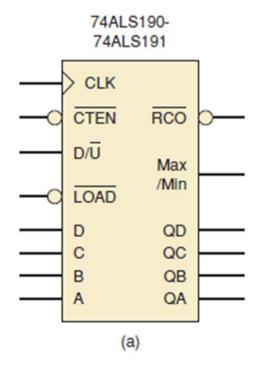

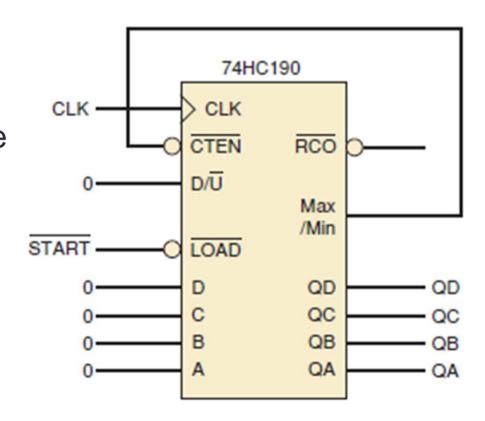

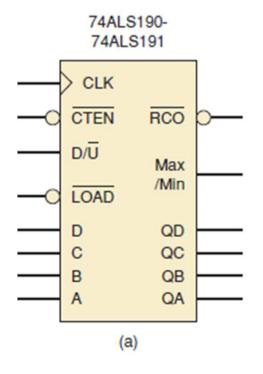

- Série 74LS190/191 (TTL) e 74HC190/191 (CMOS)

- 74LS190 → MOD-10

- 74LS191 → MOD-16

| Part<br>Number | Modulus |  |  |  |

|----------------|---------|--|--|--|

| 74ALS190       | 10      |  |  |  |

| 74ALS191       | 16      |  |  |  |

| (b)            |         |  |  |  |

#### 74ALS190-74ALS191 Function Table

| LOAD | CTEN | D/Ū | CLK | Function     |

|------|------|-----|-----|--------------|

| L    | X    | X   | X   | Asynch. Load |

| H    | L    | L   | 1   | Count up     |

| H    | L    | H   | 1   | Count down   |

| Н    | Н    | X   | X   | No change    |

| (c)  |      |     |     |              |

### Contadores UP/DOWN com PRESET

# Arranjos Multi-estágios

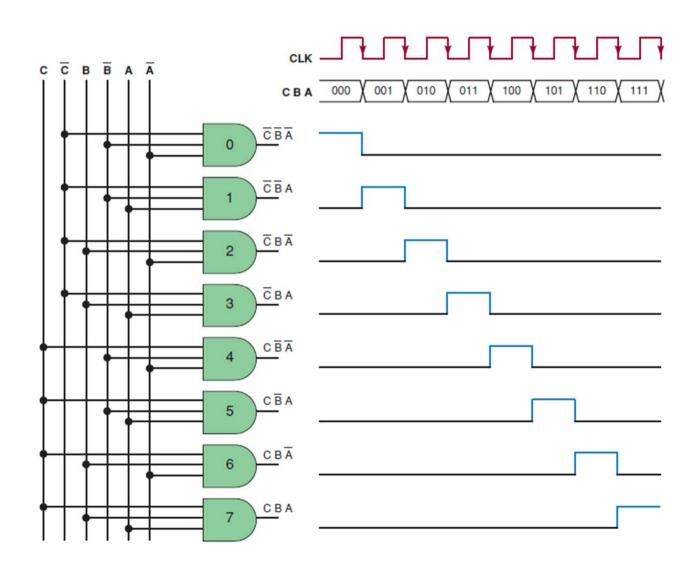

### Decodificando um Contador

- Qualquer sequência de contagem pode ser obtida

- Vejamos como analisar um contador, isto é, determinar sua sequência de estados

- Construir uma tabela de estado atual e próximo estado

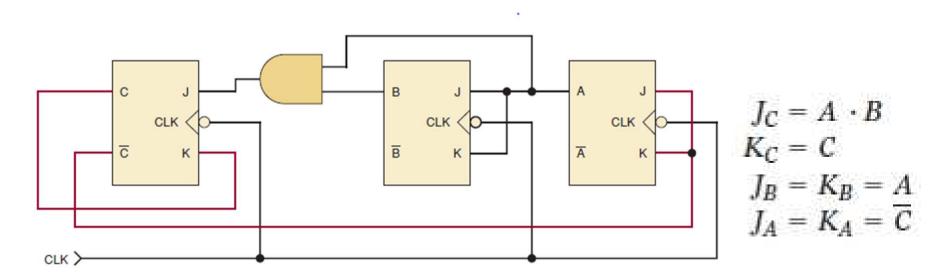

- Considere o circuito abaixo, onde as entradas de controle dos flip-flops estão ligadas segundo as expressões ao lado.

Tabela atual/próximo estado:

| PRESENT State Control Inputs |                |                |                |                |       |                |  |

|------------------------------|----------------|----------------|----------------|----------------|-------|----------------|--|

|                              |                | v              |                |                |       | v              |  |

| CBA                          | J <sub>C</sub> | K <sub>C</sub> | J <sub>B</sub> | K <sub>B</sub> | $J_A$ | K <sub>A</sub> |  |

| 0 0 0                        | 0              | 0              | 0              | 0              | 1     | 1              |  |

| 0 0 1                        | 0              | 0              | 1              | 1              | 1     | 1              |  |

| 0 1 0                        | 0              | 0              | 0              | 0              | 1     | 1              |  |

| 0 1 1                        | 1              | 0              | 1              | 1              | 1     | 1              |  |

| 1 0 0                        | 0              | 1              | 0              | 0              | 0     | 0              |  |

| 1 0 1                        | 0              | 1              | 1              | 1              | 0     | 0              |  |

| 1 1 0                        | 0              | 1              | 0              | 0              | 0     | 0              |  |

| 1 1 1                        | 1              | 1              | 1              | 1              | 0     | 0              |  |

|                              |                |                |                |                |       |                |  |

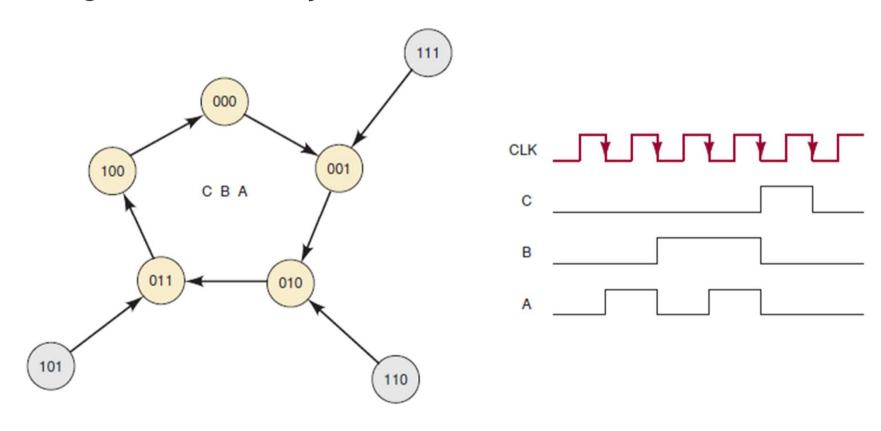

Diagrama de transição de estados

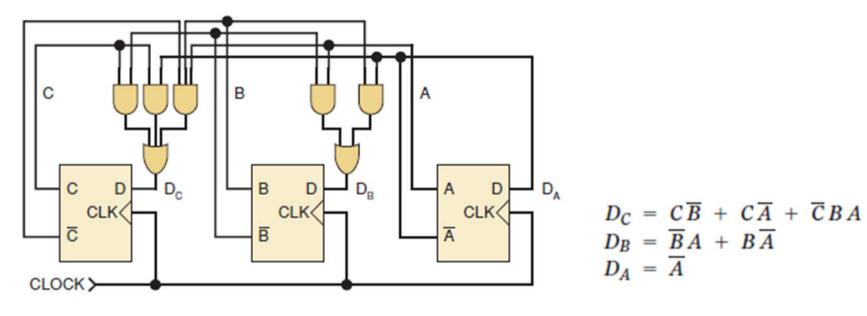

Uma análise semelhante pode ser feita se o circuito usa flip-flops tipo D:

$$D_{C} = C\overline{B} + C\overline{A} + \overline{C}BA = C(\overline{B} + \overline{A}) + \overline{C}BA$$

$$= C\overline{B}\overline{A} + \overline{C}(BA) = C \oplus (AB)$$

$$D_{B} = \overline{B}A + B\overline{A} = B \oplus A$$

$$D_{A} = \overline{A}$$

#### Tabela:

| PRES | PRESENT State |   |    | Control Inputs |       |   |   | NEXT State |  |  |  |

|------|---------------|---|----|----------------|-------|---|---|------------|--|--|--|

| C    | В             | Α | Dc | DB             | $D_A$ | C | В | Α          |  |  |  |

| 0    | 0             | 0 | 0  | 0              | 1     | 0 | 0 | 1          |  |  |  |

| 0    | 0             | 1 | 0  | 1              | 0     | 0 | 1 | 0          |  |  |  |

| 0    | 1             | 0 | 0  | 1              | 1     | 0 | 1 | 1          |  |  |  |

| 0    | 1             | 1 | 1  | 0              | 0     | 1 | 0 | 0          |  |  |  |

| 1    | 0             | 0 | 1  | 0              | 1     | 1 | 0 | 1          |  |  |  |

| 1    | 0             | 1 | 1  | 1              | 0     | 1 | 1 | 0          |  |  |  |

| 1    | 1             | 0 | 1  | 1              | 1     | 1 | 1 | 1          |  |  |  |

| 1    | 1             | 1 | 0  | 0              | 0     | 0 | 0 | 0          |  |  |  |

Se mais um bit (flip-flop D) fosse adicionado ao contador, teríamos:

$$D_D = D \oplus (ABC)$$

- Podemos projetar contadores síncronos para uma sequência arbitrária de estados

- Precisamos antes rever o funcionamento do flip-flop J-K, através da tabela de excitação:

| Transition at     | PRESENT State  | NEXT State       |   |   |

|-------------------|----------------|------------------|---|---|

| FF Output         | Q <sub>n</sub> | Q <sub>n+1</sub> | J | K |

| $0 \rightarrow 0$ | 0              | 0                | 0 | X |

| $0 \rightarrow 1$ | 0              | 1                | 1 | X |

| $1 \rightarrow 0$ | 1              | 0                | X | 1 |

| 1 → 1             | 1              | 1                | X | 0 |

- Procedimento de projeto:

- 1. Determine o número de flip-flops necessários

- 2. Desenhe o diagrama de estados desejado. Por exemplo:

3. Desenhe uma tabela que lista os estados presentes e o próximo estado de cada estado presente:

|        | PRES | SENT S | state | NE | NEXT State |   |  |  |

|--------|------|--------|-------|----|------------|---|--|--|

|        | C    | В      | A     | С  | В          | A |  |  |

| Line 1 | 0    | 0      | 0     | 0  | 0          | 1 |  |  |

| 2      | 0    | 0      | 1     | 0  | 1          | 0 |  |  |

| 3      | 0    | 1      | 0     | 0  | 1          | 1 |  |  |

| 4      | 0    | 1      | 1     | 1  | 0          | 0 |  |  |

| 5      | 1    | 0      | 0     | 0  | 0          | 0 |  |  |

| 6      | 1    | 0      | 1     | 0  | 0          | 0 |  |  |

| 7      | 1    | 1      | 0     | 0  | 0          | 0 |  |  |

| 8      | 1    | 1      | 1     | 0  | 0          | 0 |  |  |

4. Acrescente as colunas J e K para cada flip-flop:

|        | PRES | SENT | State | NEX | NEXT State |   |                |    |         |                |    |    |

|--------|------|------|-------|-----|------------|---|----------------|----|---------|----------------|----|----|

|        | C    | В    | A     | C   | В          | A | J <sub>C</sub> | Kc | $J_{B}$ | K <sub>B</sub> | JA | KA |

| Line 1 | 0    | 0    | 0     | 0   | 0          | 1 | 0              | X  | 0       | X              | 1  | X  |

| 2      | 0    | 0    | 1     | 0   | 1          | 0 | 0              | X  | 1       | X              | X  | 1  |

| 3      | 0    | 1    | 0     | 0   | 1          | 1 | 0              | X  | X       | 0              | 1  | X  |

| 4      | 0    | 1    | 1     | 1   | 0          | 0 | 1              | X  | X       | 1              | X  | 1  |

| 5      | 1    | 0    | 0     | 0   | 0          | 0 | X              | 1  | 0       | X              | 0  | X  |

| 6      | 1    | 0    | 1     | 0   | 0          | 0 | X              | 1  | 0       | X              | X  | 1  |

| 7      | 1    | 1    | 0     | 0   | 0          | 0 | X              | 1  | X       | 1              | 0  | X  |

| 8      | 1    | 1    | 1     | 0   | 0          | 0 | X              | 1  | X       | 1              | X  | 1  |

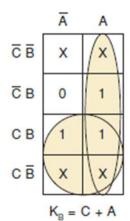

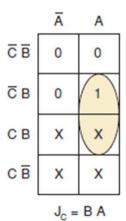

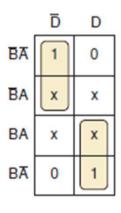

5. Projete o circuito lógico que gera as saídas J e K tendo como entradas o **estado presente**.

|    |      |    |    |    |     | Ā       | Α          |     | Ā     | A        |

|----|------|----|----|----|-----|---------|------------|-----|-------|----------|

| PF | RESE | NT |    |    |     |         |            |     |       |          |

| С  | В    | Α  | JA | KA | C B | 1       | X\         | Ū B | X     | 1        |

| 0  | 0    | 0  | 1  | X  |     |         | <u> </u>   |     | /     | <u> </u> |

| 0  | 0    | 1  | X  | 1  | ĒВ  | 1       | x /        | СВ  | X     | 1        |

| 0  | 1    | 0  | 1  | X  | ОВ  | /       | ^/         |     |       |          |

| 0  | 1    | 1  | X  | 1  |     |         |            |     |       |          |

| 1  | 0    | 0  | 0  | X  | CB  | 0       | X          | CB  | X     | 1        |

| 1  | 0    | 1  | X  | 1  |     |         |            |     | 1     | -        |

| 1  | 1    | 0  | 0  | X  | CB  | 0       | X          | CB  | \x    | 1/       |

| 1  | 1    | 1  | X  | 1  |     |         | ^          |     |       |          |

|    |      |    |    |    |     | $J_A$ : | = <u>C</u> |     | $K_A$ | = 1      |

|    |      |    |    |    |     |         |            |     |       |          |

|                        | A | A |  |  |  |  |  |

|------------------------|---|---|--|--|--|--|--|

| ĒΒ                     | 0 | 1 |  |  |  |  |  |

| ĒВ                     | X | × |  |  |  |  |  |

| СВ                     | X | х |  |  |  |  |  |

| CB                     | 0 | 0 |  |  |  |  |  |

| $J_B = \overline{C} A$ |   |   |  |  |  |  |  |

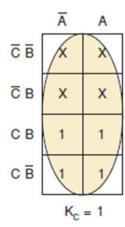

Circuito final:

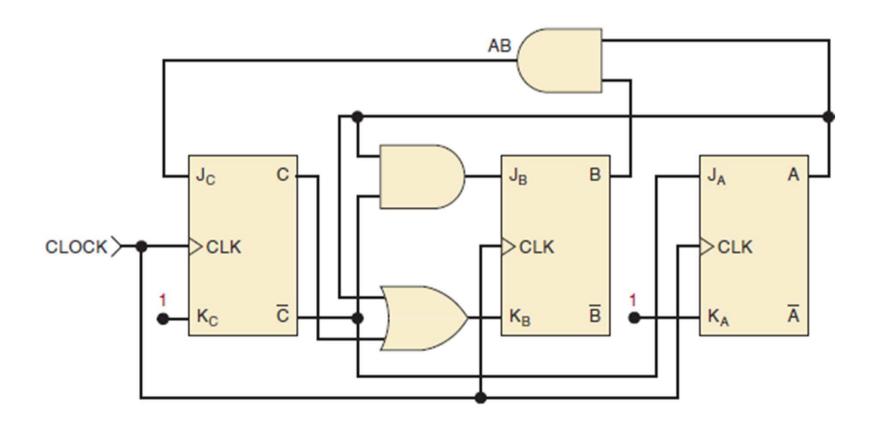

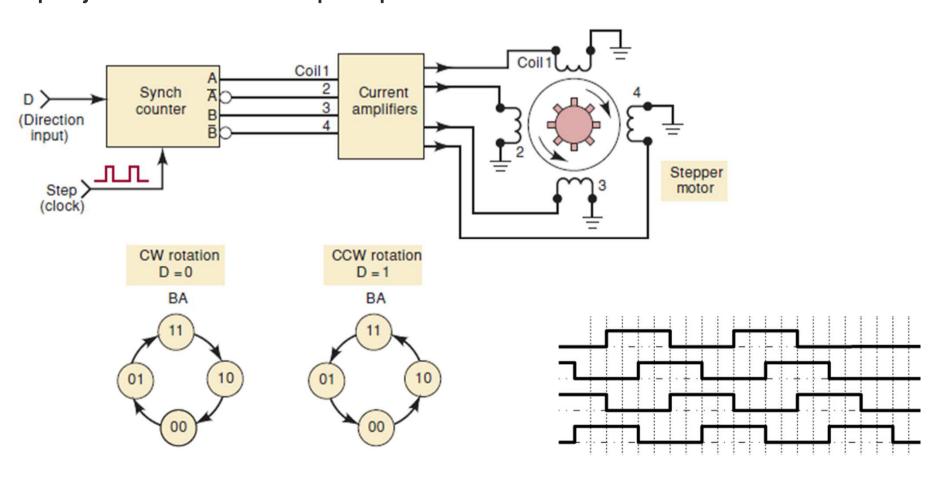

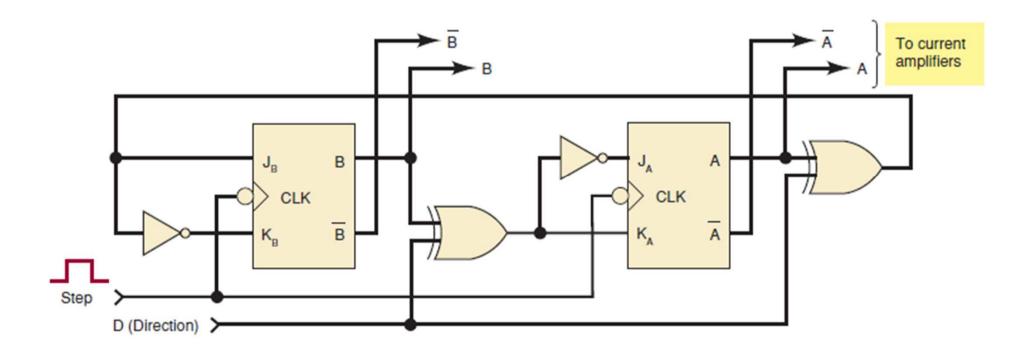

Exemplo: O driver de um motor de passo pode ser projetado usando flip-flops

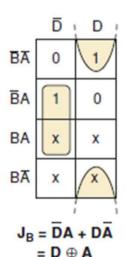

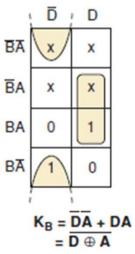

| PRES | SENT | State | NEXT | State | C              | ontrol | Inpu | Inputs |  |

|------|------|-------|------|-------|----------------|--------|------|--------|--|

| D    | В    | Α     | В    | Α     | J <sub>B</sub> | KB     | JA   | KA     |  |

| 0    | 0    | 0     | 0    | 1     | 0              | X      | 1    | X      |  |

| 0    | 0    | 1     | 1    | 1     | 1              | X      | X    | 0      |  |

| 0    | 1    | 0     | 0    | 0     | X              | 1      | 0    | X      |  |

| 0    | 1    | 1     | 1    | 0     | X              | 0      | X    | 1      |  |

| 1    | 0    | 0     | 1    | 0     | 1              | X      | 0    | X      |  |

| 1    | 0    | 1     | 0    | 0     | 0              | X      | X    | 1      |  |

| 1    | 1    | 0     | 1    | 1     | X              | 0      | 1    | X      |  |

| 1    | 1    | 1     | 0    | 1     | X              | 1      | X    | 0      |  |

| ВА | X | X |

|----|---|---|

| BA | 0 | 1 |

| ВА | 1 | 0 |

| ΒĀ | x | X |

| ,  |   |   |

$$J_{A} = \frac{\overline{DB} + DB}{\overline{D} \oplus B}$$

$$K_A = \overline{D}B + \overline{D}B$$

=  $D \oplus B$

• Circuito:

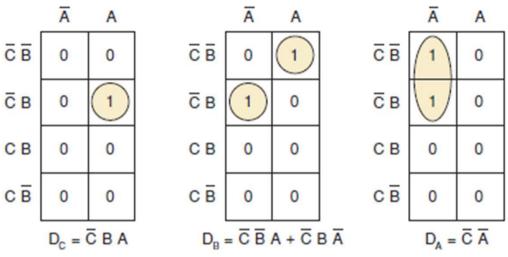

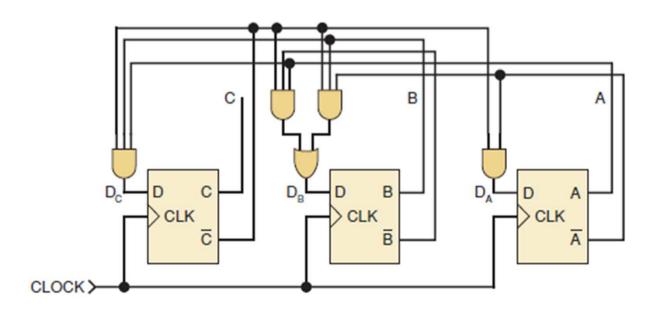

- Podemos também usar flip-flops D

- Neste caso, o próximo estado coincide com as entradas

D da sequência de flip-flops

- Exemplo: contador de três bits: (Módulo-5)

| PRESENT State |   |   | NE | XT St | ate | Control Inputs |                |    |  |

|---------------|---|---|----|-------|-----|----------------|----------------|----|--|

| С             | В | Α | С  | В     | Α   | D <sub>C</sub> | D <sub>B</sub> | DA |  |

| 0             | 0 | 0 | 0  | 0     | 1   | 0              | 0              | 1  |  |

| 0             | 0 | 1 | 0  | 1     | 0   | 0              | 1              | 0  |  |

| 0             | 1 | 0 | 0  | 1     | 1   | 0              | 1              | 1  |  |

| 0             | 1 | 1 | 1  | 0     | 0   | 1              | 0              | 0  |  |

| 1             | 0 | 0 | 0  | 0     | 0   | 0              | 0              | 0  |  |

| 1             | 0 | 1 | 0  | 0     | 0   | 0              | 0              | 0  |  |

| 1             | 1 | 0 | 0  | 0     | 0   | 0              | 0              | 0  |  |

| 1             | 1 | 1 | 0  | 0     | 0   | 0              | 0              | 0  |  |

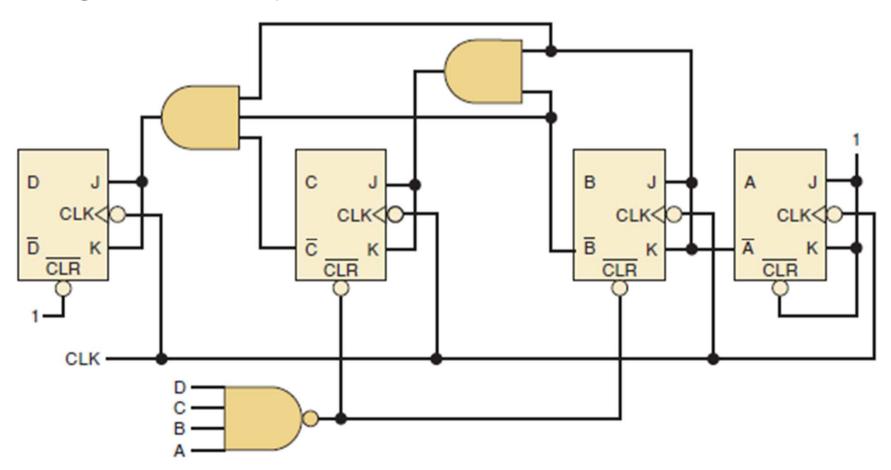

- 1. (7.21 e 7.22) Para as Figuras (a) e (b) a seguir:

- a. Desenhe o diagrama de estados para as saídas QD, QC, QB, QA

- b. Determine o módulo do contador

- c. Qual a relação entre a frequência de saída do MSB (QD) para a frequência do clock de entrada?

- d. Qual o ciclo de trabalho da forma de onda de saída (MSB)

- (7.23) No circuito dado:

- a) Desenhe o diagrama de tempo para as saídas QA, QB, QC, QD

- b) Qual é o módulo do contador?

- c) Qual é a sequência de contagem? Conta UP ou DOWN?

- d) Podemos produzir o mesmo módulo com um 74HC190? Podemos produzir a mesma sequência com um 74HC190?

- (7.24) No circuito dado:

- a) Qual é a saída QD,QC, QB, QA do contador quando \$\overline{START}\$ está em nível BAIXO?

- b) Descreva o que acontece se  $\overline{START}$  for momentaneamente para nível BAIXO e retornar para nível ALTO.

- c) Qual é o módulo-número do contador?

## 74LS160/161/162/163

| Part<br>Number | Modulus |  |  |  |  |  |

|----------------|---------|--|--|--|--|--|

| 74ALS160       | 10      |  |  |  |  |  |

| 74ALS161       | 16      |  |  |  |  |  |

| 74ALS162       | 10      |  |  |  |  |  |

| 74ALS163       | 16      |  |  |  |  |  |

| (b)            |         |  |  |  |  |  |

#### 74ALS160-74ALS163 Function Table

| CLR | LOAD | ENP | ENT | CLK | Function      | Part Numbers        |

|-----|------|-----|-----|-----|---------------|---------------------|

| L   | X    | Х   | X   | X   | Asynch. Clear | 74ALS160 & 74ALS161 |

| L   | X    | X   | X   | 1   | Synchr. Clear | 74ALS162 & 74ALS163 |

| H   | L    | X   | X   | 1   | Synchr. Load  | All                 |

| Н   | Н    | Н   | Н   | 1   | Count up      | All                 |

| H   | Н    | L   | X   | X   | No change     | All                 |

| H   | Н    | X   | L   | X   | No change     | All                 |

#### 74LS190/191 e 74HC190/191

- Série 74LS190/191 (TTL) e 74HC190/191 (CMOS)

- 74LS190 → MOD-10

- 74LS191 → MOD-16

| Part<br>Number | Modulus |  |  |

|----------------|---------|--|--|

| 74ALS190       | 10      |  |  |

| 74ALS191       | 16      |  |  |

| (b)            |         |  |  |

#### 74ALS190-74ALS191 Function Table

| LOAD | CTEN | D/Ū | CLK | Function     |

|------|------|-----|-----|--------------|

| L    | X    | X   | X   | Asynch. Load |

| H    | L    | L   | 1   | Count up     |

| Н    | L    | H   | 1   | Count down   |

| Н    | Н    | X   | X   | No change    |

| (c)  |      |     |     |              |

- (7.25) Desenhe o esquemático para criar um contador módulo-6 que utiliza:

- a) O controle CLEAR em um 74LS160

- b) O controle CLEAR em um 74LS162

- (7.26) Desenhe o esquemático para criar um contador módulo-6 que produza a seguinte sequência de contagem:

- a) 1,2,3,4,5,6 e repete, com um 74LS162

- b) 5,4,3,2,1,0 e repete, com um 74LS190

- c) 6,5,4,3,2,1 e repete, com um 74LS190

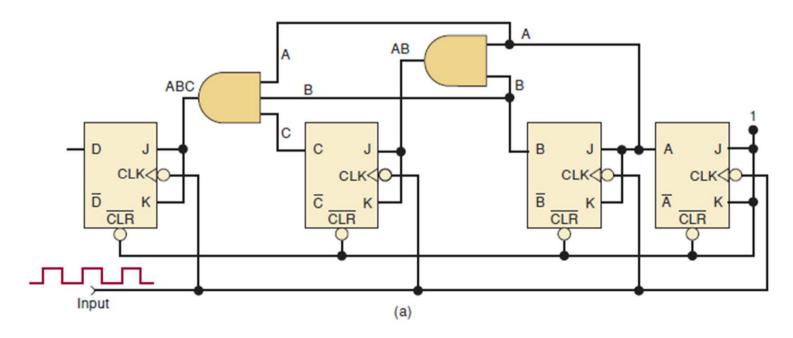

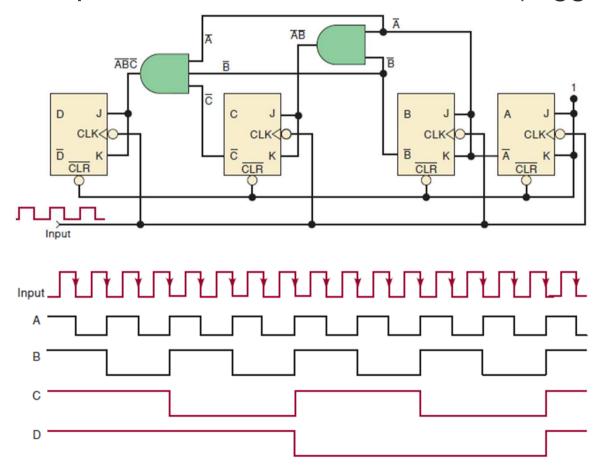

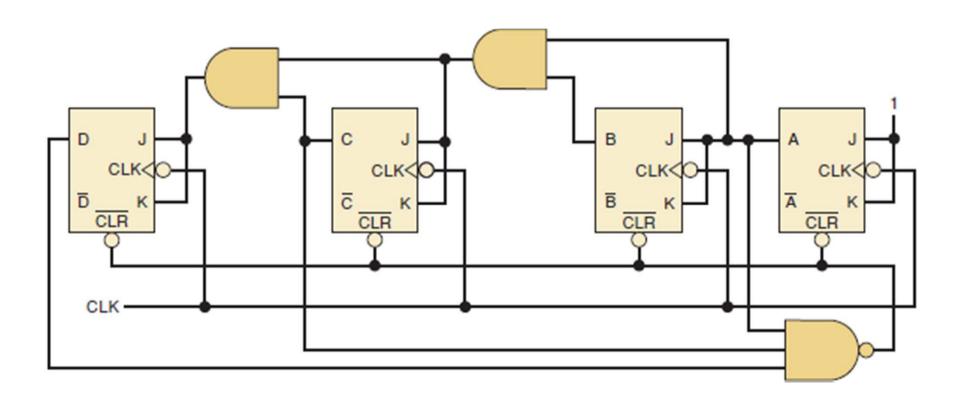

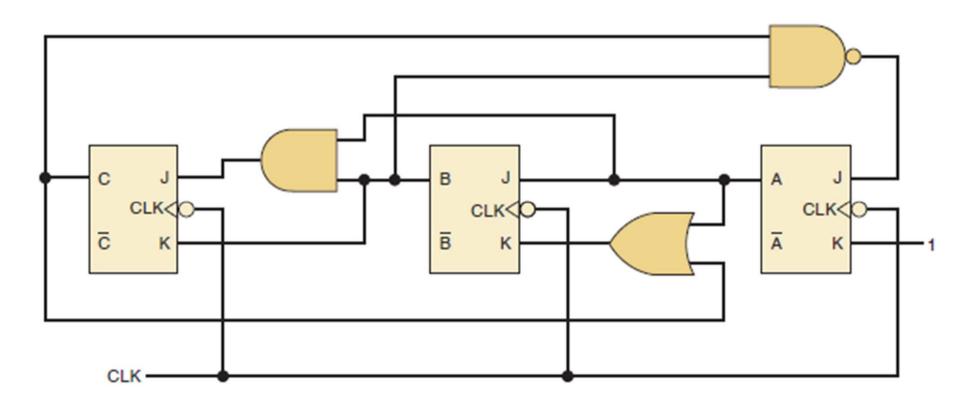

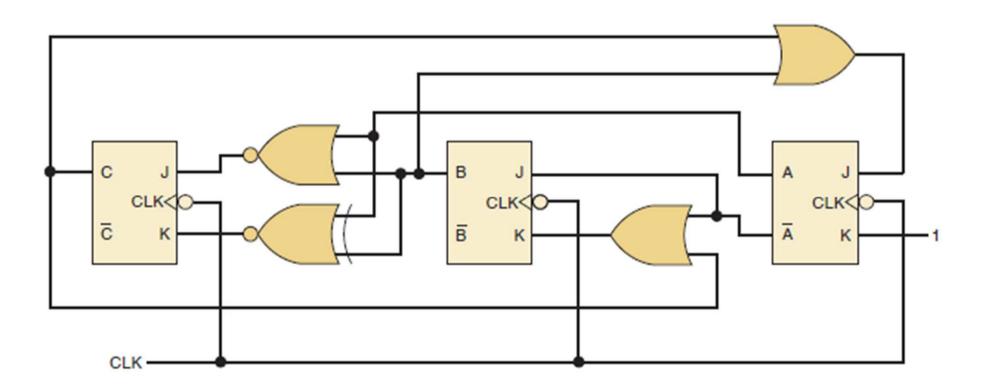

• (7.37) Analise o contador síncrono abaixo. Desenhe o seu diagrama de tempo e determine o seu módulo

• (7.38) Analise o contador síncrono abaixo. Desenhe o seu diagrama de tempo e determine o seu módulo

• (7.39) Analise o contador síncrono abaixo. Desenhe o seu diagrama de tempo e determine o seu módulo

• (7.40) Analise o contador síncrono abaixo. Desenhe o seu diagrama de tempo e determine o seu módulo

Exercícios do Livro

Sistemas Digitais - Princípios e Aplicações - Ronald Tocci - 10a Ed.

pág. 277

7.1, 7.2, 7.3, 7-4, 7.5, 7.6, 7.7, 7.11, 7.13, 7.14, 7.18, 7.19, 7.35, 7.36, 7.37, 7.38, 7.39